| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | ||

| 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 13 | 14 | 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 | 25 | 26 |

| 27 | 28 | 29 | 30 |

- NRS

- Overlap capacitance

- 문턱전압

- MOSFET Gate Capacitance

- BSIM4 diffusion resistor

- HV Gate Capacitance

- fringing capacitance

- BSIM4 parasitic capacitance

- Threshold voltage

- short channel effect

- junction area capacitance

- junction capacitance

- leakage current

- 반전증폭기

- MOSFET

- SCE

- pocket implant

- opamp

- 벌크 전하 효과

- Flipflop

- MOSFET parasitic capacitance

- BSIM4 manual

- LDMOS Gate Capacitance

- BSIM4

- Gate Capacitance

- bulk charge effect

- CGD

- diffusion resistor

- MOSFET NRD NRS

- 플립플롭

- Today

- Total

날아라팡's 반도체 아카이브

LOD Effect(=STI STRESS EFFECT) 본문

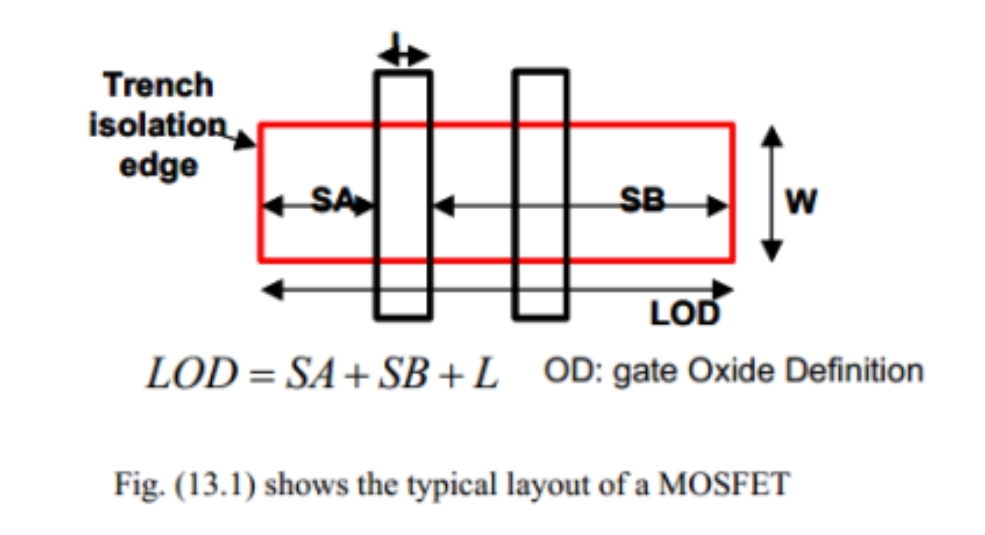

Layout에 기인하는 effect 중에서 LOD Effect를 알아보자.

구글링을 해보면 LOD의 full name이 아래 2가지로 나온다.

1. Length Of Diffusion

2. Length of Oxide Definition

여러 논문을 참고했을때, 2번 정의가 올바른 표현같다.

아무래도 LOD라는게 Source&Drain 영역, 즉 Diffusion 영역을 나타내다 보니 1번 정의로 표현된 듯 하다.(아래 그림을 확인해보면 된다.)

그렇다면 LOD는 어떻게 정의되는가?

LOD는 poly gate의 length와 source/drain 가로 길이의 합으로 정의된다. 즉, LOD는 위에 빨간색으로 표된 active 영역의 가로 길이를 말한다. 이 LOD 증감에 따라 device 에 가해지는 stress가 달라진다.

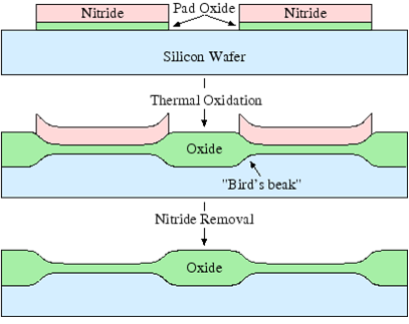

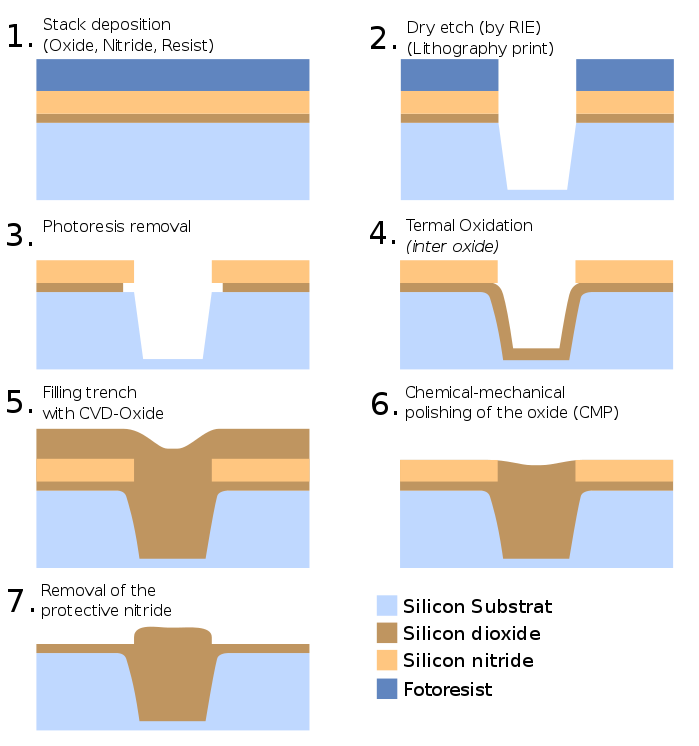

LOD Effect를 설명하기 앞서 Isolation 기술의 변천에 대해 알아두면 좋다.

먼저 Isolation이란 소자간 전기적인 영향을 줄이기 위해 물리적인 공간을 분리하는 기술이라고 생각하면된다.

* LOCOS(Local oxidation On Silicon)

* STI(Shallow Trench Isolation)

초기에 LOCOS 공정이 산업 전반에 사용됐으나, 소자 미세화에 따라 STI 공정이 도입되었다.

STI 공정은 집적도 측면에서 효율적이었으나 소자 특성에 영향을 주게 됐다. STI 구조로 인해 Silicon에 인력(혹은 장력)이 가해지게 된다.

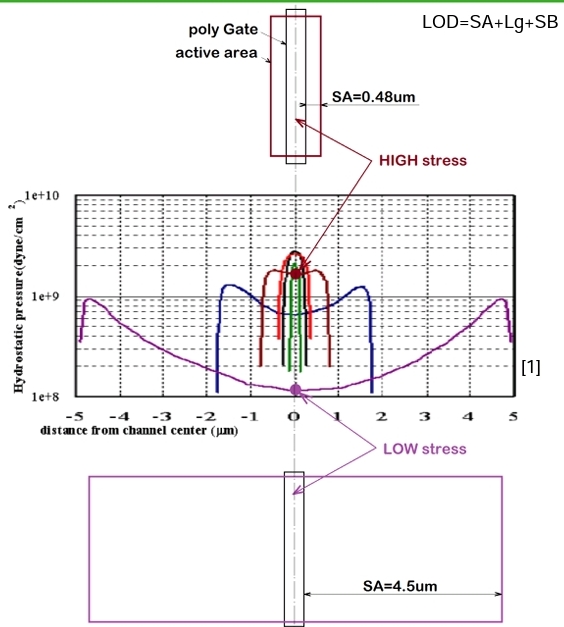

LOD 변화에 따른 Stress 곡선은 아래와 같다.

총 6개의 선이 보이는데 각각 LOD가 다르다.

위 그래프를 해석해보자.

그러기 위해선 용어 정의가 필요하다.

- Edge : STI와 OD interface

- Center : Poly gate의 2분의 1지점

해석 1) LOD 감소 -> Edge stress 증가

해석 2) LOD 감소 -> Center stress 증가

해석 3) LOD가 감소하면 Center stress 증가율이 Edge stress 증가율보다 크다.

참고) 논문에서는 1/LOD trend를 가진다고 표현한다. 이것은 해석 1, 2에서도 확인할 수 있듯이 LOD와 Stress 가 반비례 관계이기 때문이다.

그 결과로 STI stress effect는 Drain current와 Treshold voltage에 영향을 주며 원인은 아래와 같다.

- Band structure 변동에 따른 mobility 변화

- Doping profile 변동에 따른 Vt 변화

* 이 부분은 다른 논문을 통해 확인할 필요가 있다. 나중에 확인하도록 하자.

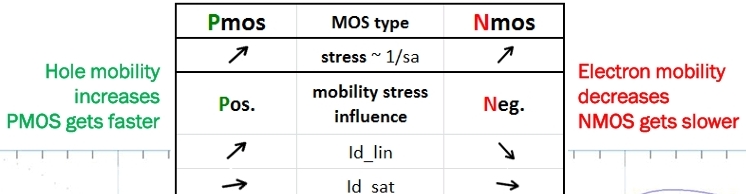

STI stress에 따른 cuurent와 Vt trend가 N/PMOS가 서로 다르다.

NMOS : Id 감소 / Vt 증가

PMOS : Id 증가 / Vt 감소

* 하지만 이것도 불변의 진리가 아니라 Tech 혹은 공정 process마다 다르다.

LOD와 Current 관계를 정리하면 아래와 같다.

'Device Modeling' 카테고리의 다른 글

| BSIM4 Manual : Bulk charge effect에 대한 고찰(2)_channel length dependency (0) | 2021.06.08 |

|---|---|

| BSIM4 Manual : Bulk charge effect에 대한 고찰(1) (0) | 2021.06.08 |

| BSIM4 Manual : Source/Drain Resistance Model에 대한 고찰(2) (0) | 2021.06.07 |

| BSIM4 Manual : Source/Drain Resistance Model에 대한 고찰(1) (0) | 2021.06.06 |

| Gate Overlap capacitance의 Bias dependency (1) | 2021.04.27 |