| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 |

- Gate Capacitance

- MOSFET NRD NRS

- fringing capacitance

- opamp

- 벌크 전하 효과

- 문턱전압

- bulk charge effect

- MOSFET Gate Capacitance

- leakage current

- diffusion resistor

- BSIM4

- BSIM4 parasitic capacitance

- Overlap capacitance

- BSIM4 diffusion resistor

- 플립플롭

- pocket implant

- 반전증폭기

- CGD

- junction area capacitance

- HV Gate Capacitance

- Flipflop

- MOSFET parasitic capacitance

- Threshold voltage

- NRS

- short channel effect

- SCE

- BSIM4 manual

- LDMOS Gate Capacitance

- junction capacitance

- MOSFET

- Today

- Total

날아라팡's 반도체 아카이브

Junction capacitance in BSIM4 본문

이전 포스팅에서 MOSFET의 parasitic capacitance 성분에 대해 다뤘습니다.

자세한 내용은 아래 포스팅을 확인 바랍니다.

2021.08.17 - [Device Modeling] - Parasitic capacitance modeled in BSIM4

Parasitic capacitance modeled in BSIM4

BSIM4에 모델링되어 있는 capacitance는 아래 vertical view처럼 표시할 수 있다. 그림 (a)가 MOSFET의 parasitic capacitance 성분을 나타낸 것이며, 그림 (b)는 channel 방향에 따른 Doping 농도를 표시한 것이..

zzoonijjoons.tistory.com

이번 포스팅은 Junction capacitance에 대한 내용을 다루려고 합니다.

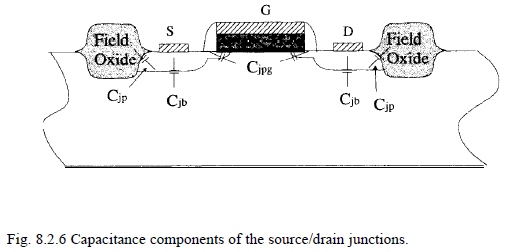

Junction capacitance는 Bottom area capacitance/Isolation edge perimeter capacitance/Gate edge perimeter capacitance로 분류합니다.(용어는 교재마다 다르게 표현할 수 있습니다.)

이것을 그림으로 표시하면 다음과 같습니다.

그림마다 용어가 다르게 표현할 수 있지만 끝 첨자에 'p'가 붙은 것은 perimeter, 'pg'가 붙은 것은 gate perimeter로 생각하면 됩니다.

굳이 이렇게 3가지로 나누는 이유는 각 면이 접하는 부분이 다르고, 이로 인해 capacitance가 다를 수 밖에 없기 때문에 분류하게 됐다고 생각하면 됩니다.

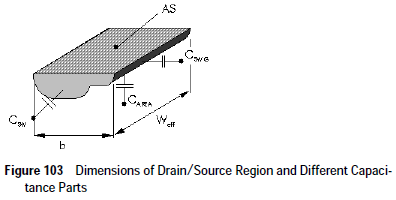

위 그림을 3차원 도면으로 표현하면 아래와 같습니다.

아래 그림에 표시된 기호들은 capacitance 계산식에 사용되는 것이니 자세히 확인하길 바랍니다.

이제 모든 성분을 하나로 합치면 아래와 같은 식으로 정리됩니다.

이제 각 성분별로 어떤 parameter로 구현이 되는지 확인해봅시다.

# Bottom area capacitance

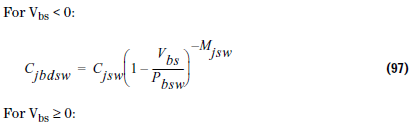

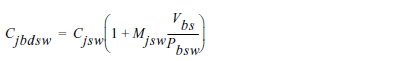

# Isolation edge perimeter capacitance

# Gate edge perimeter capacitance

이 모든걸 합쳐 하나의 Cj로 표현하면 아래와 같이 표현할 수 있죠.

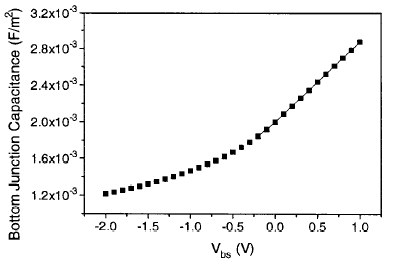

그렇다면 실제로 측정하게 되면 어떤 CV plot을 볼 수 있을까요?

하나의 예로 Bottom area capacitance를 보여드리겠습니다.(다른 junction capacitance 성분들도 값에 차이가 있지만 동일한 경향을 보입니다.)

위 그래프를 보면 전압이 negative로 갈수록 capacitance가 작아지는 것을 볼 수 있습니다.

원인은 다음 flow를 따라서 생각해보면 됩니다.

1. 전압이 음의 값으로 커진다.

2. PN Junction의 Depletion width가 커진다.

3. C=E*A/d이므로 'd'인 Depletio width가 커지므로 capacitance는 작아진다.

SPICE Modeling을 하다보면 Capacitance 계산에 사용되는 parameter(M,PB,CJ 등)의 대략적인 값이 얼마인지 알아두는 것이 도움이 됩니다. 물론 공정마다 상이한 값을 가지고 있지만 비슷한 order 수준에서 크게 벗어나지 않습니다.

1um CMOS technology 기준으로 각 parameter별 값은 아래와 같으니 확인하길 바랍니다.

'Device Modeling' 카테고리의 다른 글

| MOSFET의 Gate Capacitance 특성 그래프 이해 (3) | 2021.10.09 |

|---|---|

| Parasitic capacitance modeled in BSIM4 (0) | 2021.08.17 |

| BSIM4 Manual: Diffusion resistor (0) | 2021.08.07 |

| Leakage current 확인 방법 (2) | 2021.07.31 |

| BSIM4 Manual : Bulk charge effect에 대한 고찰(2)_channel length dependency (0) | 2021.06.08 |