Notice

Recent Posts

Recent Comments

Link

250x250

| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 |

Tags

- Gate Capacitance

- 벌크 전하 효과

- MOSFET NRD NRS

- Threshold voltage

- opamp

- 플립플롭

- pocket implant

- CGD

- 문턱전압

- MOSFET parasitic capacitance

- diffusion resistor

- 반전증폭기

- BSIM4 parasitic capacitance

- MOSFET Gate Capacitance

- junction area capacitance

- BSIM4 diffusion resistor

- leakage current

- junction capacitance

- short channel effect

- Flipflop

- HV Gate Capacitance

- LDMOS Gate Capacitance

- NRS

- bulk charge effect

- Overlap capacitance

- MOSFET

- BSIM4 manual

- BSIM4

- SCE

- fringing capacitance

Archives

- Today

- Total

날아라팡's 반도체 아카이브

Leakage current 확인 방법 본문

728x90

회로 설계에 있어 전력 소모를 최소화하는 것은 가장 중요하게 고려해야할 사항 중 하나이다.

전력 중에서도 대기 전력을 최소화하는 것이 바로 그 중에 하나이다.

대기 전력을 줄이기 위해선 소자의 leakage를 줄여야한다.

이처럼 MOSFET(특히 Logic Tr.)을 모델링하는 SPICE Modeling 엔지니어는 다음과 같은 leakage를 고려해야 한다.

(이 외에도 고려해야할 leakage 성분이 많을 수 있다.)

- Gate leakage

- Channel leakage

- Gate Induced Drain Leakage(GIDL)

그렇다면 이 leakage current를 확인하기 위해 MOSFET의 노드에 어떤 전압을 인가해야 할까?

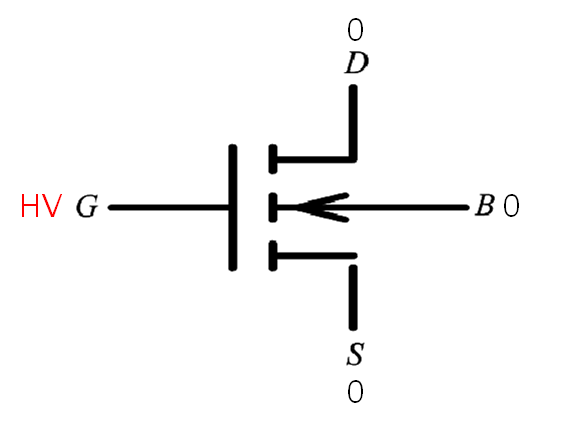

이것을 MOSFET symbol에 각 전압을 표시하려고 한다. 작성 편의를 위해 동작 전압 수준을 HV로, GND 전압을 0으로 표시하겠다.

1. Gate leakage

2. Channel leakage

3. Gate Induced Drain Leakage(GIDL)

위와 같이 각 노드에 전압을 인가했으면 HSPICE의 다음의 명령어를 사용하여 각 노드별 전류를 확인할 수 있다.

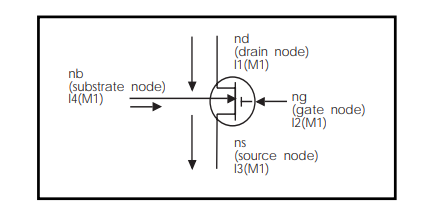

만약 netlist에서 위 MOSFET을 'M1'이라고 명명했다면 아래와 같이 입력하면 된다.

.print i1(M1) i2(M1) i3(M1) i4(M1)

참고로 i1, i2, i3, i4는 각각 drain, gate, source, body 노드의 전류를 의미한다.

728x90

'Device Modeling' 카테고리의 다른 글

| Parasitic capacitance modeled in BSIM4 (0) | 2021.08.17 |

|---|---|

| BSIM4 Manual: Diffusion resistor (0) | 2021.08.07 |

| BSIM4 Manual : Bulk charge effect에 대한 고찰(2)_channel length dependency (0) | 2021.06.08 |

| BSIM4 Manual : Bulk charge effect에 대한 고찰(1) (0) | 2021.06.08 |

| BSIM4 Manual : Source/Drain Resistance Model에 대한 고찰(2) (0) | 2021.06.07 |

Comments