| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 |

- 반전증폭기

- MOSFET NRD NRS

- 문턱전압

- opamp

- pocket implant

- 벌크 전하 효과

- leakage current

- fringing capacitance

- LDMOS Gate Capacitance

- MOSFET Gate Capacitance

- bulk charge effect

- 플립플롭

- BSIM4 manual

- MOSFET

- BSIM4 diffusion resistor

- CGD

- BSIM4 parasitic capacitance

- MOSFET parasitic capacitance

- NRS

- HV Gate Capacitance

- Flipflop

- diffusion resistor

- short channel effect

- SCE

- junction area capacitance

- junction capacitance

- Threshold voltage

- BSIM4

- Gate Capacitance

- Overlap capacitance

- Today

- Total

날아라팡's 반도체 아카이브

Threshold Voltage에 영향을 끼치는 효과(2)_Channel width effect 본문

Treshold voltage에 영향을 끼치는 요소들은 분류하면 다음과 같습니다.

- Substrate Doping effect : Vertical non-Uniform doping effects / Lateral non-Uniform doping effects

- Channel length effect : Normal short channel effects / Reverse short channel effects

- Channel width effect : Normal Narrow width effects / Reverse narrow width effects

- body & bulk charge effect : Body bias effect and bulk charge effect

이전 포스팅에서 "Substrate Doping effect", "Channel width effect","body & bulk charge effect" 내용을 다뤘으니 아래 포스팅를 참고하시면 됩니다.

2021.06.17 - [DEVICE PHYSICS] - Threshold Voltage에 영향을 끼치는 효과(1)_Non uniform doping effect

Threshold Voltage에 영향을 끼치는 효과(1)_Non uniform doping effect

문턱전압에 영향을 주는 효과는 일반적으로 6개로 구분할 수 있습니다. 다만 새로운 공정 기술의 도입과 미세화로 인해 추가적인 영향이 있을 수 있으나 그런 부분은 논외로 하겠습니다. 문턱전

zzoonijjoons.tistory.com

2021.06.17 - [DEVICE PHYSICS] - Threshold Voltage에 영향을 끼치는 효과(2)_Channel length effect

Threshold Voltage에 영향을 끼치는 효과(2)_Channel length effect

Treshold voltage에 영향을 끼치는 요소들은 분류하면 다음과 같습니다. - Substrate Doping effect : Vertical non-Uniform doping effects / Lateral non-Uniform doping effects - Channel length effect :..

zzoonijjoons.tistory.com

2021.06.04 - [DEVICE PHYSICS] - MOSFET에서 Vt와 Body effect

MOSFET에서 Vt와 Body effect

*해당 내용은 Chenming Calvin Hu 박사의 "Modern Semiconductor Devices for Integrated Circuits"에서 반도체 물리 내용을 정리한 것입니다. 오늘은 MOSFET Vt와 Body effect의 관계에 대하여 알아보겠습니다...

zzoonijjoons.tistory.com

2021.06.07 - [DEVICE PHYSICS] - Bulk charge effect(벌크 전하 효과)

Bulk charge effect(벌크 전하 효과)

이번 포스팅은 Bulk charge effect(이하 벌크 전하 효과)에 대해 서술하고자 합니다. 벌크 전하 효과는 소자 물리 교재에서 그 내용을 찾아보는 게 쉽지 않습니다.. 하지만 BSIM4 메뉴얼을 보면 문턱 전

zzoonijjoons.tistory.com

이번 포스팅은 channel width effect에 대하여 알아보도록 하겠습니다.

본격적으로 channel width effect를 분석하기 전에 숙지해야할 공정이 있습니다.

바로 Isolation 공정입니다. 후술하겠지만 channel width effect는 Isolation 종류(LOCOS 또는 STI)에 따라 영향을 받습니다.

2020.09.02 - [Device Modeling] - Isolation 개요

Isolation 개요

해당 글은 Isolation에 대한 기본적인 개념과 이에 대한 구조와 필요성을 알아보고자 한다. <요약> 1. 물리적인 Isolation은 thick oxide로, 전기적인 Isolation은 Well 영역 형성으로 진행한다. 2. Isolation 변..

zzoonijjoons.tistory.com

그럼 이제 Isolation에 대한 기본적인 이해가 됐다고 생각하고 설명하겠습니다.

문턱전압의 channel width effect는 channel width가 감소함에 따라 문턱전압이 증가하거나 감소하는 현상을 의미합니다. 각각을 Narrow width effect와 Reverse narrow width effect라고 합니다.

1. Narrow width effect

Narrow width effect(이하 NWE)는 channel width가 감소함에 따라 문턱전압이 증가하는 현상입니다.

이것은 주된 원인은 Isolation 공정 중에서 "LOCOS 구조로 인한 채워야 할 Charge 양의 증가"로 인한 것입니다.

이를 설명하기 위해 LOCOS 공정이 적용된 MOSFET의 단면도를 가져오겠습니다.

LOCOS 공정을 하게 되면 마치 새의 부리처럼 "Bird's beak"가 생겨 게이트 전극을 파고들게 됩니다.

MOSFET의 게이트는 W인데 LOCOS의 bird's bea로 인해 게이트 전극은 delta W만큼 양쪽에 추가가 되어 Wm이 됩니다.

만약 게이트 전극에 전압을 가하게 된다면 MOSFET 정의상 W에 해당하는 charge보다 더 많은 charge를 끌어모아야 합니다. 추가적인 전하량은 FOX 아래 표시된 영역만큼 필요합니다.

Channel width가 충분히 클 때 FOX 아래 존재하는 영역이 차지하는 비중이 작지만 width가 작아질수록 그 비중이 커져 문턱전압이 커지게 되는 것입니다.

LOCOS 공정은 소자가 미세화되지 않았던 시절에 사용하던 기술입니다.

최근에는 집적도를 높이기 위해 STI 공정을 사용하므로 narrow width effect를 보기 어렵습니다.(물론 legacy 공정에선 사용할 수 있습니다...)

2. Reverse narrow width effect

Reverse narrow width effect(이하 RNWE)는 channel width가 감소함에 따라 문턱전압이 감소하는 현상입니다.

이것은 주된 원인은 Isolation 공정 중에서 "STI 구조"로 때문입니다.

이를 설명하기 위해 STI 공정이 적용된 MOSFET의 단면도를 가져오겠습니다.

STI 구조는 코너 쪽이 sharp하여 높은 전기장이 가해집니다. 이에 따라 코너 근처에 + charge 이온이 쌓이게 됩니다.

이렇게 되면 + charge로 인해 게이트 전압이 작아도 충분한 channel이 형성됩니다.

결국 문턱전압이 감소하게 되는 것이죠.

여기서 기억할 점은 PMOS도 STI 코너 부근에 + charge 이온이 쌓인다는 점입니다.

PMOSFET은 hole이 channel의 캐리어이므로 더 많은 게이트 전압을 가해야합니다.

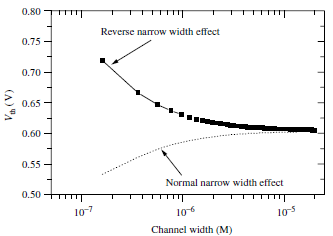

NWE와 RWNE를 그래프로 표현하면 다음과 같습니다.

이 그래프를 통해 문턱전압의 width 경향을 보고 어떤 공정이 사용됐는지 파악할 수 있습니다.

아래 그림에서 reverse와 normal graph가 서로 다르게 표현되어있습니다.

width가 감소할수록 Vt가 증가하는 것이 normal narrow width effect이며, 반대가 reverse narrow width effect입니다.

'DEVICE PHYSICS' 카테고리의 다른 글

| MOS Capacitance 자료 (0) | 2022.03.04 |

|---|---|

| LDMOS 소자의 이해 (2) | 2021.09.03 |

| Threshold Voltage에 영향을 끼치는 효과(2)_Channel length effect (1) | 2021.06.17 |

| Threshold Voltage에 영향을 끼치는 효과(1)_Non uniform doping effect (1) | 2021.06.17 |

| Bulk charge effect(벌크 전하 효과) (0) | 2021.06.07 |