| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | |||

| 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| 12 | 13 | 14 | 15 | 16 | 17 | 18 |

| 19 | 20 | 21 | 22 | 23 | 24 | 25 |

| 26 | 27 | 28 | 29 | 30 | 31 |

- pocket implant

- HV Gate Capacitance

- BSIM4 parasitic capacitance

- fringing capacitance

- SCE

- Flipflop

- 문턱전압

- opamp

- NRS

- 벌크 전하 효과

- MOSFET parasitic capacitance

- leakage current

- BSIM4 manual

- BSIM4 diffusion resistor

- diffusion resistor

- MOSFET Gate Capacitance

- MOSFET

- Gate Capacitance

- junction capacitance

- LDMOS Gate Capacitance

- bulk charge effect

- junction area capacitance

- 반전증폭기

- 플립플롭

- Threshold voltage

- BSIM4

- CGD

- Overlap capacitance

- MOSFET NRD NRS

- short channel effect

- Today

- Total

날아라팡's 반도체 아카이브

Gate를 POLY-Si으로 구성하는 이유 본문

MOS CAPACITOR에 대한 포스팅에서 Gate가 Metal로 되어 있을 때를 분석하였다. 하지만 실제론 Metal이 아닌 POLY-Si으로 Gate를 구성한다.(최근에는 여러가지 이유로 POLY-Si에서 Metal로 회귀했다고 한다.)

그렇다면 Gate 구성 물질로 왜 POLY-Si을 사용하게 됐을까?

POLY-Si의 장점을 Metal과 비교하여 정리하면 아래와 같다.

1. Metal에 비해 녹는점이 높아 안정적인 동작이 가능하며 공정 프로세스 사용의 범위가 넓어진다.

2. POLY-Si 농도를 조절하여 Threshold voltage를 조정할 수 있다.

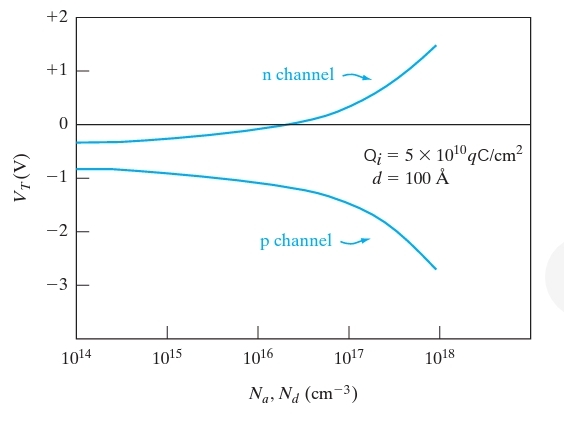

Circuit은 전력 효율 등의 이유로 CMOS 집적방식으로 구현된다. 그런데 Gate가 Metal로 되어 있으면 NMOS 및 PMOS의 Threshold voltage가 농도 증가에 따라 반대 경향을 가진다.

Circuit 동작 구현에 있어 device의 적절한 동작점(Threshold voltage)을 찾아 설계하는게 중요하다.

그렇다면 POLY-Si으로 Gate가 구성된 NMOS 및 PMOS의 Vt를 구해보고 기판 농도에 따른 Vt 변화를 확인해보자.

먼저 POLY-Si Gate로 구성된 N/PMOS는 아래와 같다.

계산하기 전에 아래와 같은 가정이 필요하다.

첫번째 가정은 POLY-Si이 고농도로 도핑되어 있어 n+, p+ POLY-Si의 Fermi level이 각각 Conduction band 및 Valence band에 위치하는 Degenerated semiconductor로 만들어져 있다는 것이다.

두번째 가정은 Oxide내 Interface charge가 없다.

세번째 가정은 intrinsic fermi level은 정확히 bandgap의 절반이다.

네번째 가정은 Band-gap narrowing은 없다. 도핑을 많이 하면 band gap이 줄게되며 이것을 Band-gap narrowing이라고 하지만 계산에서는 이 효과를 무시한다.

Substrate와 Poly 모두 silicon이므로 band-gap이 동일하며 N+ POLY, P+ POLY, NMOS 기판, PMOS 기판의 에너지대역도를 그리면 아래와 같다.

이 그림들을 이용하여 NMOS의 Gate를 N+ POLY로, PMOS Gate를 P+ POLY로 사용할 때의 Vt를 계산해보자.

Vt 계산 결과는 Metal일 때와 달리 식에 work function을 포함하지 않고 band-gap을 포함하므로 Vt를 설계하기 편해진다.(Work function을 측정할 필요가 사라진다.)

이제 Gate가 POLY-Si으로 구성될 때 기판 농도에 따른 Vt 변화는 아래와 같다.

POLY-Si을 사용하면 PMOS의 Vt도 최적화할 수 있는 doping level을 찾을 수 있다. 결국 전체적인 Vt를 위 방법을 이용하여 감소시킬 수 있다.

Vt가 대략 0.7V 수준이던 시절엔 POLY-Si을 사용하여 0.3V까지 줄일 수 있어 획기적이었다. 하지만 기술의 발전으로 Vt를 줄이는 획기적인 방법이 나타났다. 이에 따라 최근에는 N+/P+ POLY를 만들기 위한 추가 공정의 메리트가 감소하여 잘 사용되지 않는다.

'DEVICE PHYSICS' 카테고리의 다른 글

| MOSFET Scaling (0) | 2020.11.04 |

|---|---|

| Short channel MOSFET_short channel로 인한 Effect (0) | 2020.11.03 |

| MOSFET_Subthreshold 특성 (0) | 2020.11.02 |

| MOSFET 동작 Mechanism_Basic (1) | 2020.11.01 |

| Multiplier VS Finger on MOSFET (1) | 2020.09.14 |